-

- 联系我们

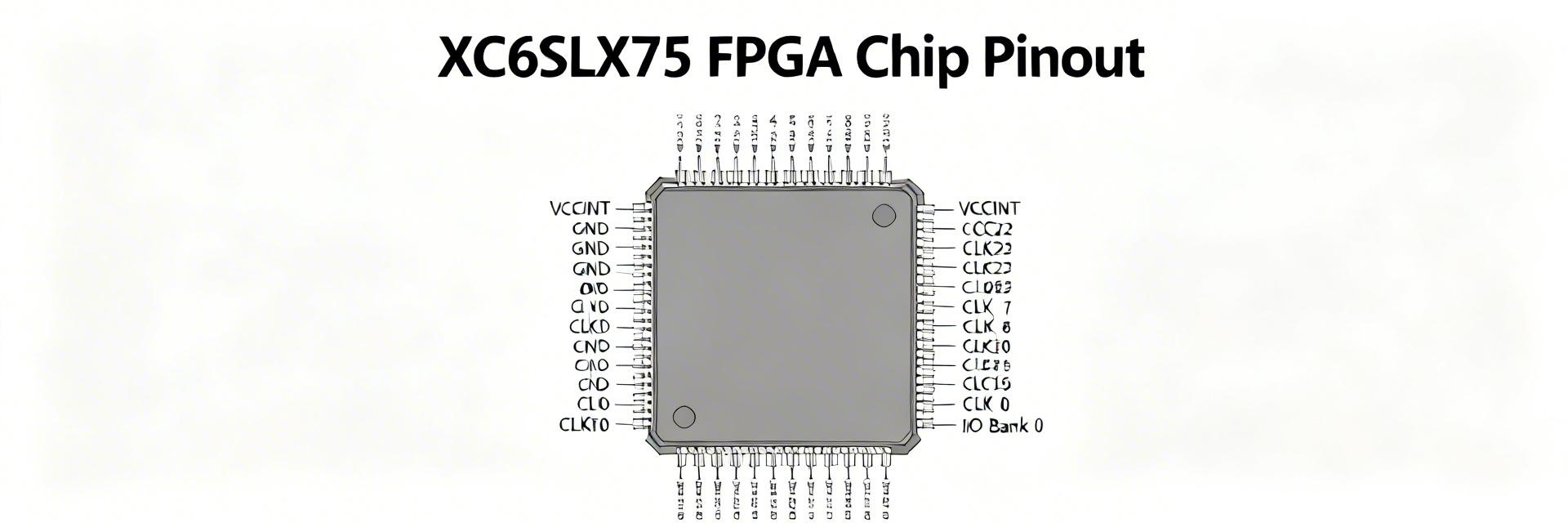

XC6SLX75 Data Sheet Analysis: Key Specs, Pinout & Limits

נקודות מפתח (סיכום GEO)

- צפיפות ממוטבת: 74,637 תאי לוגיקה (Logic Cells) מספקים את האיזון האידיאלי עבור בקרה תעשייתית בטווח בינוני ללא עלויות קצה גבוהות.

- שלמות אות (Signal Integrity) משופרת: מספר בנקים של I/O תומכים בתקני מתח מגוונים (1.2V עד 3.3V) לגישור פרוטוקולים חלק.

- יעילות תרמית: תהליך ייצור מתקדם של 45 ננומטר מפחית את צריכת החשמל הסטטית בעד 20% בהשוואה לדורות קודמים.

- ביצועי DSP: 132 פרוסות DSP48A1 ייעודיות מאיצות אלגוריתמים מורכבים לסינון ובקרת מנוע.

על פי דף הנתונים (datasheet) הרשמי של ה-XC6SLX75, התקן זה מספק עשרות אלפי שווי-ערך ל-LUT ומספר מגה-ביטים של Block RAM, מה שמציב אותו בדיוק בקטגוריית ה-FPGA בצפיפות בינונית המתאימה לבקרה, DSP מתון ומשימות I/O מותאמות אישית. מאמר זה נותן פירוט תמציתי וממוקד מהנדס של דף הנתונים של XC6SLX75, כך שמתכננים יוכלו למצוא במהירות מפרטים מרכזיים, מגבלות פריסת פינים (pinout) ומגבלות תכנון מעשיות לפני תחילת המימוש.

המטרה היא חילוץ מידע בר-ביצוע: הצבעה על הטבלאות והפרמטרים המדויקים שעליכם לאמת בדף הנתונים, הדגשת מכשולים נפוצים (חוקי ריבוי מסילות מתח, הפחתת הספק תרמית), ומתן רשימות בדיקה וחישובי דוגמה שניתן ליישם ישירות בתכנון טרום-סיליקון ובאימות פוסט-סיליקון.

1 — סקירת רכיב ותמונת מצב של מפרטים עיקריים

סקירה כללית של ארכיטקטורת FPGA טיפוסית

1.1 — סיכום המכשיר בשורה אחת ויישומים מיועדים

נקודה: XC6SLX75 הוא רכיב לוגי ניתן לתכנות בצפיפות בינונית המיועד ללוגיקת בקרה, DSP מתון ומערכות הדורשות I/O גמיש.

עדות: טבלאות המשאבים בדף הנתונים מפרטות את מחלקת המכשיר, ספירת המשאבים והערות יישום מומלצות.

הסבר: התייחסו למכשיר זה כאל "סוס עבודה" כאשר אתם זקוקים ליותר משאבים מאשר בחלקי קצה נמוך, אך ללא ההספק והעלות של מכשירי קצה גבוה — אידיאלי עבור מישורי בקרה בטלקום, בקרת מנוע וגישור פרוטוקולים.

1.2 — טבלת מפרט לייחוס מהיר

| מפרט | ערך (XC6SLX75) | תועלת למשתמש |

|---|---|---|

| לוגיקה (LUTs) | 74,637 | מטפל ב-2-3 מעבדי soft-core מורכבים בו-זמנית. |

| Block RAM | 3,096 Kbits | חציצת נתונים בקיבולת גבוהה עבור פריימים של וידאו 1080p. |

| פרוסות DSP | 132 (DSP48A1) | פעולות MAC 18x18 בזמן אמת לסינון אותות. |

| מקסימום I/O למשתמש | עד 408 פינים | קישוריות נרחבת עבור מערכי חיישנים מרובים. |

בידול מקצועי: XC6SLX75 מול XC6SLX45

בחירת הצפיפות הנכונה מונעת עלויות של תכנון יתר תוך הבטחת מרווח ביטחון (headroom) מספיק.

| תכונה | XC6SLX45 (סטנדרטי) | XC6SLX75 (ביצועים) | יתרון |

|---|---|---|---|

| תאי לוגיקה | 43,661 | 74,637 | +71% צפיפות לוגית |

| Block RAM | 2,088 Kb | 3,096 Kb | טוב יותר עבור FIFO גדולים |

| יחס עלות/לוגיקה | קו בסיס | ממוטב | החזר השקעה (ROI) גבוה יותר למשימות DSP |

2 — צלילה עמוקה למפרטי חשמל ותזמון

2.1 — מאפייני DC ודירוגים מקסימליים מוחלטים

נקודה: אשר את מסילות ה-VCC הפועלות, טווחי מתח IO ומגבלות מקסימום מוחלטות לפני חיבור החשמל.

הסבר: סמן כל מסילה הדורשת רצף (sequencing) קפדני. טיפ למהנדס: VCCINT (1.2V) חייב להיות יציב לפני VCCAUX כדי להבטיח את פתיחת שערי הקונפיגורציה כראוי.

2.2 — פרמטרי תזמון ודרגות מהירות

נקודה: סגירת תזמון (Timing closure) תלויה בדרגת המהירות של המכשיר (-2, -3, או -3N).

טיפ מקצועי: תמיד תכננו עבור דרגת מהירות -2 כדי לאפשר הגירה קלה יותר לרכיבים מהירים ויקרים יותר אם סגירת התזמון הופכת לצוואר בקבוק בשלב מאוחר של הפיתוח.

3 — פריסת פינים, אפשרויות מארז ומגבלות I/O

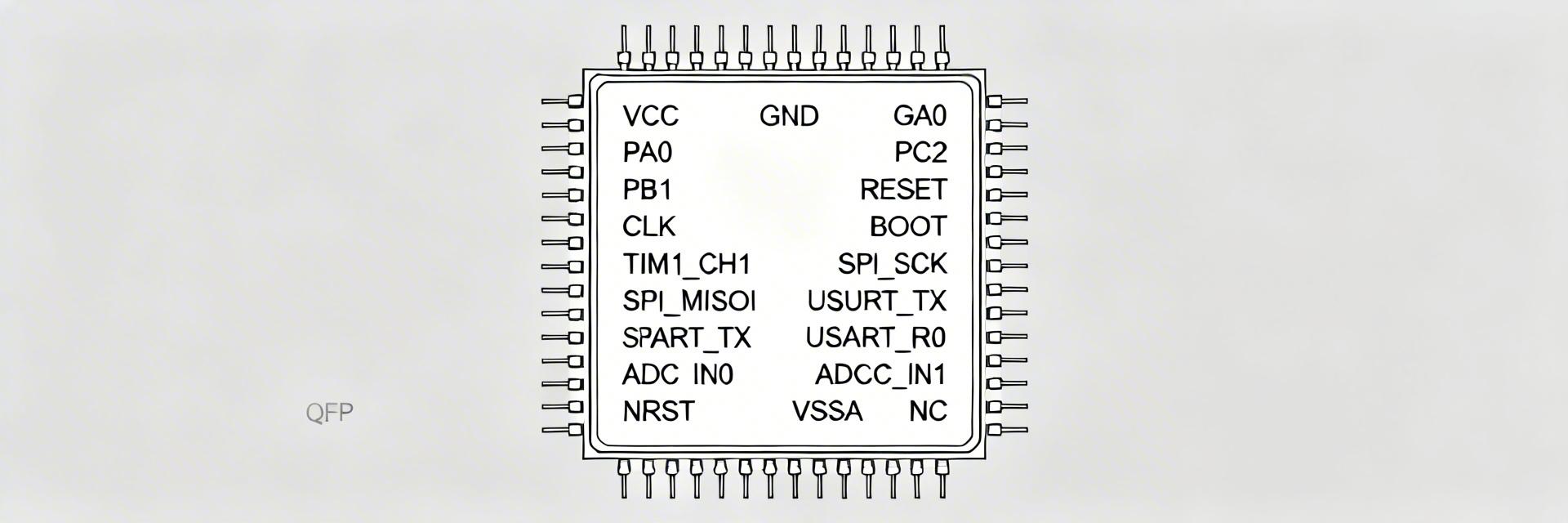

אסטרטגיית בנקים של I/O

ה-XC6SLX75 כולל עד 6 בנקים. מומלץ לקבץ זוגות LVDS מהירים בבנקים 0 ו-2 להפצת שעון אופטימלית. הימנעו מערבוב לוגיקה של 3.3V ו-1.8V באותו בנק כדי למנוע הולכת דיודה של ESD.

4 — הספק, מגבלות תרמיות ואמינות

נקודת מבט של מהנדס: ניהול תרמי

מאת: מרקוס ו. (ארכיטקט מערכות בכיר)

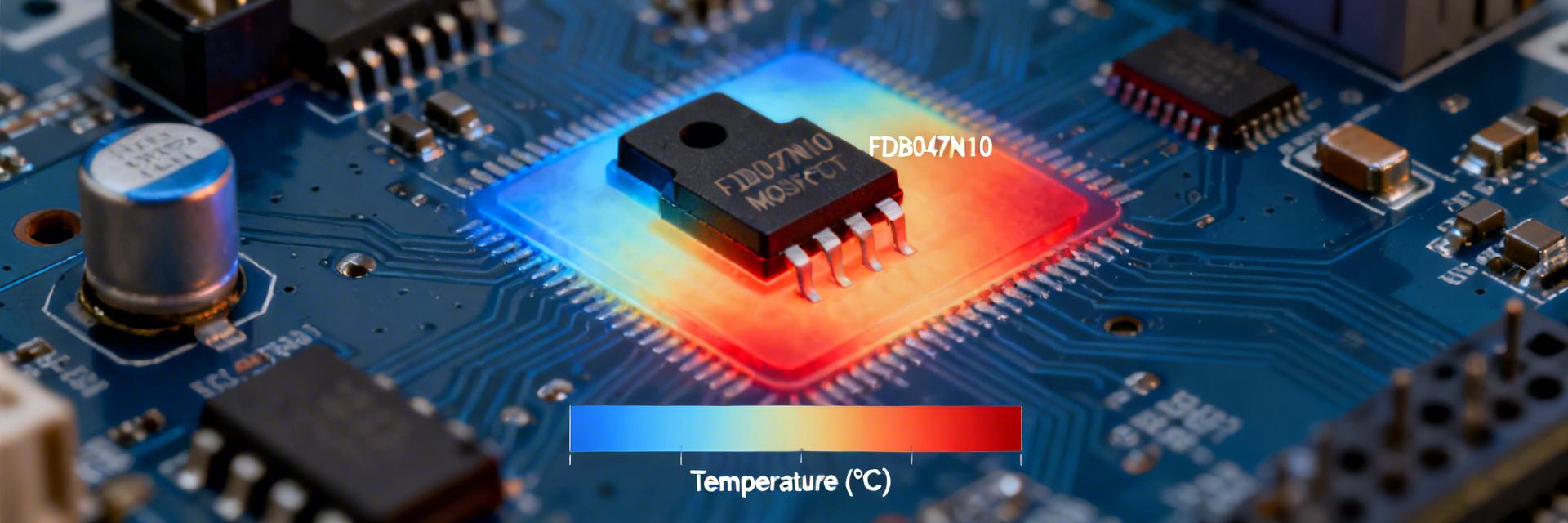

"ראיתי עיצובי XC6SLX75 רבים שנכשלים בשטח כי המתכנן התעלם מ-Theta-JA באוויר עומד. בניצול מלא, חלק זה יכול למשוך מעל 2W. ללא זרימת אוויר של 200 LFM או פד תרמי ייעודי המחובר למישור אדמה מוצק, טמפרטורות הצומת יכולות לעלות מעל 85 מעלות צלזיוס במהירות, מה שמוביל לריצוד תזמון (jitter) בלתי צפוי."

5 — מקרי בוחן טיפוסיים

5.1 — דוגמה 1: שער (gateway) תעשייתי לטווח בינוני

שימוש ב-XC6SLX75 כגשר בין ISA מסורתי ל-PCIe מודרני, תוך ניהול 4 ערוצי RS-485. ה-BRAM מנוצל עבור מאגרי חבילות מעגליים כדי להבטיח אפס אובדן נתונים בתקופות של פסיקות (interrupts) רבות.

6 — רשימת בדיקה למימוש

- אימות רצף הפעלת VCCINT, VCCAUX, VCCO.

- בדיקת תאימות מתח בנקים עבור תקני ה-I/O המיועדים.

- הרצת XPower Analyzer עם קצבי מיתוג משוערים.

- אישור נגדי סיום (termination resistors) עבור קווי LVDS מהירים.

סיכום

- דף הנתונים של XC6SLX75 מאשר כי המכשיר הוא FPGA בצפיפות בינונית עם עשרות אלפי שווי-ערך ל-LUT ומספר מגה-ביטים של Block RAM — מתאים לבקרה ויישומי DSP מתונים.

- מגבלות עיקריות לאימות: חוקי VccIO לכל בנק, מתחי מקסימום מוחלטים, טבלאות תזמון לפי דרגת מהירות והנחיות להפחתת הספק תרמית שחולצו מדף הנתונים.

- צעדים הבאים מעשיים: בניית תקציב הספק מודולרי, הקצאת בנקים של I/O בשלב מוקדם, יישום שיטות עבודה תרמיות מומלצות ב-PCB והרצת תוכנית אימות פוסט-סיליקון ממוקדת.

שאלות נפוצות

מה עלי לחפש קודם כל בדף הנתונים של ה-XC6SLX75?

התחילו עם טבלאות משאבי המכשיר ומאפייני ה-DC: אשרו את המספרים המדויקים של לוגיקה/BRAM/DSP, טווחי מתח ליבה ו-I/O, אפשרויות מארז ודירוגים מקסימליים מוחלטים.

כיצד ניתן לאמת את מגבלות המתח של XC6SLX75 במהלך העלאת החומרה (bring-up)?

מדדו כל מסילת כוח בנפרד בהפעלה הראשונה, השוו מול טווחי הפעולה המומלצים, ובצעו בדיקות זרם סטטי לפני הפעלת ה-I/O.

אילו פרמטרי תזמון הם קריטיים לניתוח תזמון סטטי (STA)?

אמתו את מגבלות תדר שעון הליבה, חלונות ה-setup וה-hold של הקלט/פלט, והתנהגות נעילת ה-PLL. תמיד כללו את מקרי הקצה הגרועים ביותר של PVT.

- SN74AVCH8T245DGVR Specs Deep Dive: Performance & Limits

- FDB047N10 MOSFET: Latest Benchmarks & Thermal Data

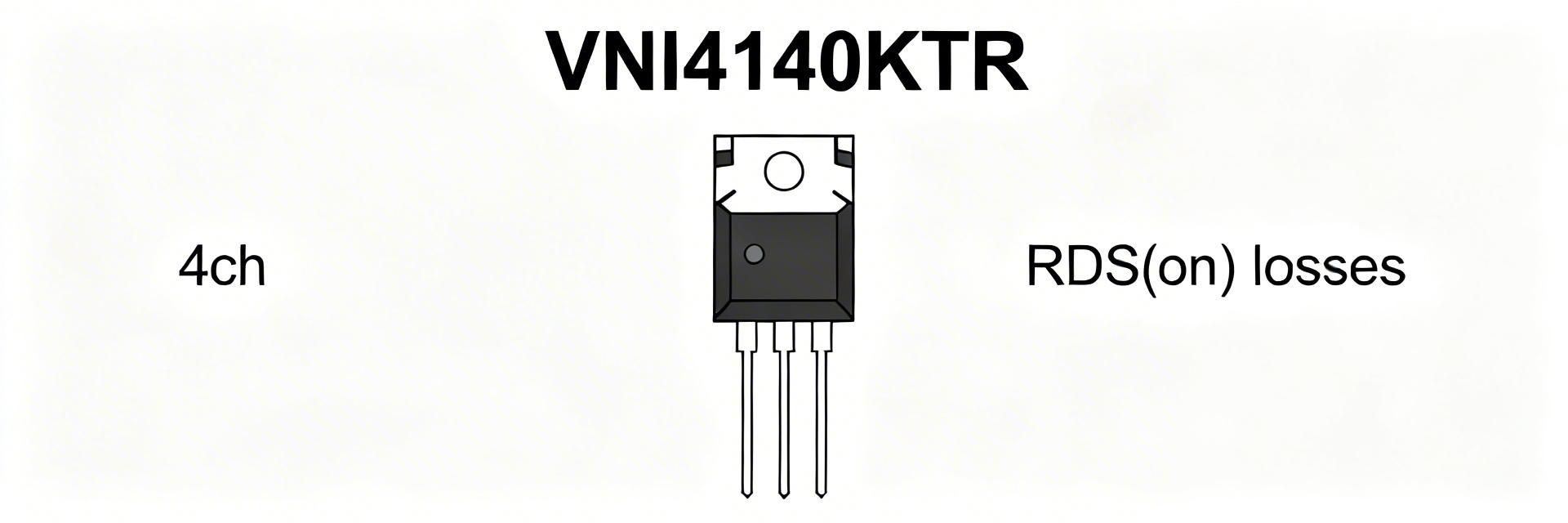

- VNI4140KTR Performance Report: RDS(on), Current and Losses

- STM8S003F3U6TR Datasheet: Key Specifications, Pinout & Quick PDF

- XC6SLX75 Data Sheet Analysis: Key Specs, Pinout & Limits

- PM5990B-FEI Performance Report: Key Metrics & Specs

- RC0402JR-07100KL Datasheet: Measured Specifications & Yield

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220