-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

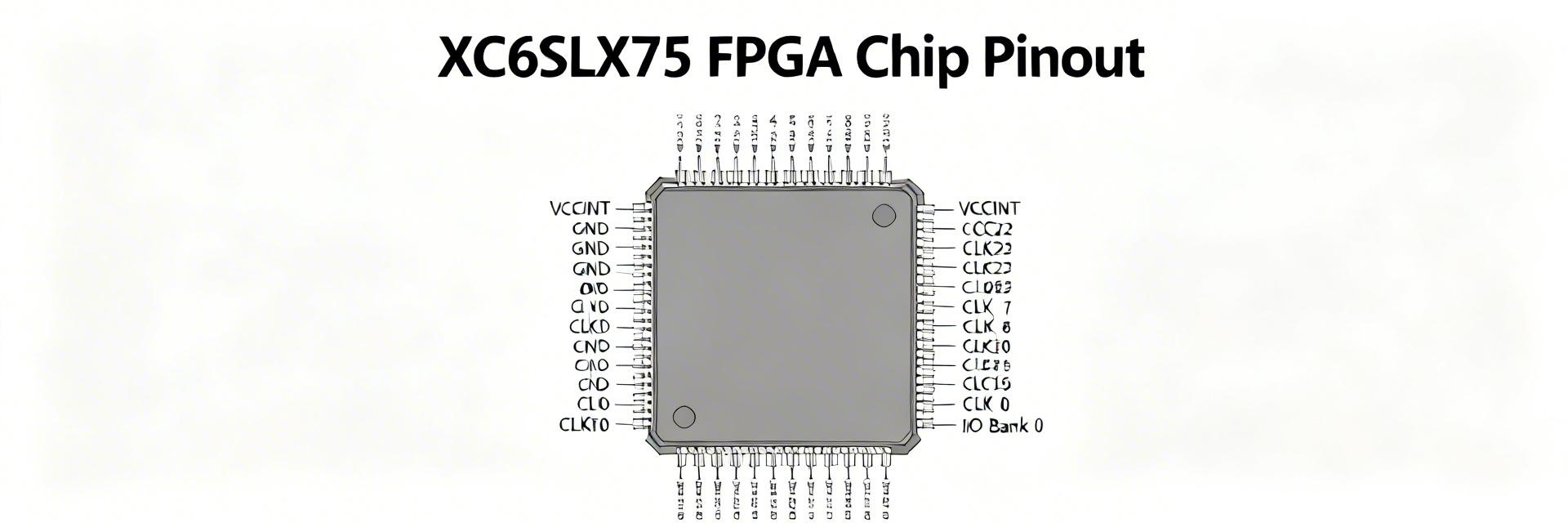

XC6SLX75 Datasheet Analysis: Key Specs, Pinout & Limits

Key Takeaways (GEO Summary)

- Optimized Density: 74,637 Logic Cells provide the ideal balance for mid-range industrial control without high-end costs.

- Enhanced Signal Integrity: Multiple I/O banks support diverse voltage standards (1.2V to 3.3V) for seamless protocol bridging.

- Thermal Efficiency: Advanced 45nm process reduces static power consumption by up to 20% compared to previous generations.

- DSP Performance: 132 dedicated DSP48A1 slices accelerate complex filtering and motor control algorithms.

Per the official XC6SLX75 datasheet, this device delivers on the order of tens of thousands of LUT-equivalents and multiple megabits of block RAM, placing it squarely in the mid-density FPGA class suitable for control, moderate DSP, and custom I/O tasks. This article gives a concise, engineer-focused breakdown of the XC6SLX75 datasheet so designers can quickly find key specs, pinout constraints, and practical design limits before starting implementation.

The goal is actionable extraction: call out the exact tables and parameters you must verify in the datasheet, highlight common gotchas (multi-rail rules, thermal derating), and provide checklists and example calculations that can be applied directly in pre-silicon planning and post-silicon validation.

1 — Device Overview & Key Specs Snapshot

Typical FPGA Architecture Overview

1.1 — One-line device summary and targeted applications

Point: XC6SLX75 is a mid-density programmable logic device intended for control logic, moderate DSP, and systems requiring flexible I/O.

Evidence: Datasheet resource tables list device class, resource counts, and recommended application notes.

Explanation: Treat this device as the workhorse when you need more resources than low-end parts but without the power and cost of high-end devices — ideal for telecom control planes, motor control, and protocol bridging.

1.2 — Quick reference spec table

| Spec | Value (XC6SLX75) | User Benefit |

|---|---|---|

| Logic (LUTs) | 74,637 | Handles 2-3 complex soft-core processors simultaneously. |

| Block RAM | 3,096 Kbits | High-capacity data buffering for 1080p video frames. |

| DSP Slices | 132 (DSP48A1) | Real-time 18x18 MAC operations for signal filtering. |

| Max User I/Os | Up to 408 pins | Extensive connectivity for multi-sensor arrays. |

Professional Differentiation: XC6SLX75 vs. XC6SLX45

Choosing the right density prevents over-engineering costs while ensuring enough headroom.

| Feature | XC6SLX45 (Standard) | XC6SLX75 (Performance) | Advantage |

|---|---|---|---|

| Logic Cells | 43,661 | 74,637 | +71% Logic Density |

| Block RAM | 2,088 Kb | 3,096 Kb | Better for Large FIFOs |

| Cost/Logic Ratio | Baseline | Optimized | Higher ROI for DSP tasks |

2 — Electrical & Timing Specs Deep-Dive

2.1 — DC characteristics and absolute maximum ratings

Point: Confirm operating VCC rails, IO voltage ranges and absolute-max limits before connecting power.

Explanation: Flag any rails that require strict sequencing. Engineer's Hint: VCCINT (1.2V) must be stable before VCCAUX to ensure proper configuration gate-up.

2.2 — Timing parameters and speed grades

Point: Timing closure depends on device speed grade (-2, -3, or -3N).

Pro-tip: Always design for -2 speed grade to allow for easier migration to faster, more expensive bins if timing closure becomes a bottleneck in late-stage development.

3 — Pinout, Package Options & I/O Limits

I/O Bank Strategy

The XC6SLX75 features up to 6 banks. Grouping high-speed LVDS pairs in Bank 0 and 2 is recommended for optimal clock distribution. Avoid mixing 3.3V and 1.8V logic in the same bank to prevent ESD diode conduction.

4 — Power, Thermal & Reliability Limits

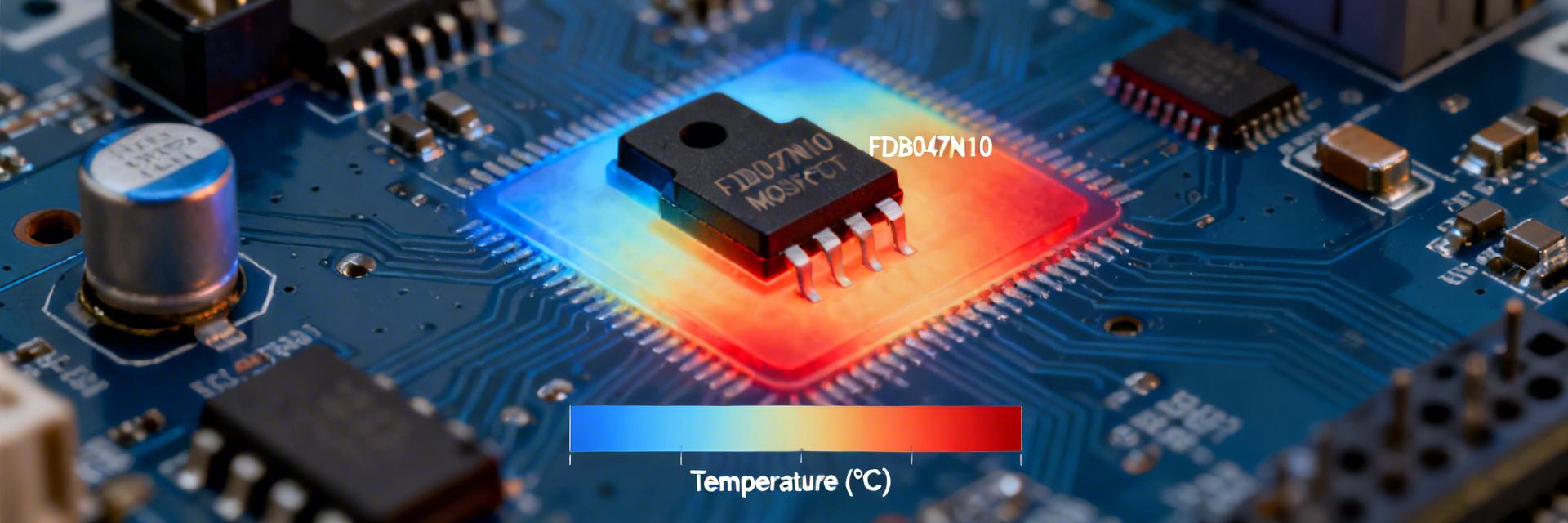

Engineer's Perspective: Thermal Management

By: Marcus V. (Senior Systems Architect)

"I’ve seen many XC6SLX75 designs fail in the field because the designer ignored Theta-JA in stagnant air. At full utilization, this part can pull 2W+. Without 200 LFM airflow or a dedicated thermal pad connected to a solid ground plane, junction temperatures can exceed 85°C quickly, leading to unpredictable timing jitter."

5 — Typical Use Cases

5.1 — Example 1: Mid-range industrial gateway

Using the XC6SLX75 as a bridge between Legacy ISA and modern PCIe, while managing 4x RS-485 channels. The BRAM is utilized for circular packet buffers to ensure zero data loss during high-interrupt periods.

6 — Implementation Checklist

- Verify VCCINT, VCCAUX, VCCO power-up sequence.

- Check bank voltage compatibility for target I/O standards.

- Run XPower Analyzer with estimated toggle rates.

- Confirm termination resistors for high-speed LVDS lines.

Summary

- XC6SLX75 datasheet confirms the device as a mid-density FPGA with tens of thousands of LUT-equivalents and multiple megabits of block RAM—suitable for control and moderate DSP applications.

- Key limits to verify: per-bank VccIO rules, absolute max voltages, speed-grade timing tables, and thermal derating guidance extracted from the datasheet.

- Practical next steps: build a componentized power budget, assign I/O banks early, apply PCB thermal best practices, and run a focused post-silicon validation plan.

Frequently Asked Questions

What should I look for first in the XC6SLX75 datasheet?

Start with the Device Resources and DC Characteristics tables: confirm exact logic/BRAM/DSP counts, core and I/O voltage ranges, package options, and absolute maximum ratings.

How do I verify XC6SLX75 voltage limits during hardware bring-up?

Measure each power rail individually at first power-up, compare against recommended operating ranges, and perform static current checks before enabling I/O.

Which timing parameters are critical for STA?

Validate core clock frequency limits, input/output setup and hold windows, and PLL lock behavior. Always include worst-case PVT corners.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- MAX3232CPWR Performance Report: Real RS-232 Specs & Insights

- 74HC123PW Complete Specs & Datasheet Quick-Reference

- SN74HC126PW Availability: Technical & Stock Snapshot

- SN74HC126PW Datasheet Deep Dive: Key Specs & Tests

- MAX96712GTB/V+T Availability and Pricing: Market Report

- ADS1015 ADC Deep Specs Report: Pinout & Performance

- Marvell 88SE9235A1 Deep Specs & Real-World Benchmarks

- STM32F103C8T6 Blue Pill: Benchmarks & Field Results

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220