-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

AD7606BSTZ Performance Report: Key ADC Metrics Explained

The AD7606BSTZ delivers up to ~95.5 dB SNR and 16-bit nominal resolution across eight simultaneous channels at 200 kS/s per channel—making it a leading multi-channel ADC for industrial data acquisition. This article explains the ADC performance metrics engineers care about, how those metrics are measured for the AD7606BSTZ, and practical implications for design choices. The goal is a data-first, reproducible guide to interpreting SNR, ENOB, THD+N, noise floor and crosstalk for real systems.

Point: Engineers evaluating multi-channel front ends need clear performance definitions before bench validation. Evidence: datasheet typical figures and vendor application notes set expectations for measured SNR/ENOB and harmonic behavior. Explanation: by aligning test setup and analysis with those published conditions (input amplitude, clock source, temperature), you get reproducible results and can map measured deviations to layout, clocking or front-end errors.

1 — Background: AD7606BSTZ at a glance (background introduction)

Device overview and target applications

Point: The AD7606BSTZ is a multi-channel successive approximation (SAR) ADC family member optimized for simultaneous sampling. Evidence: architecture is SAR with eight simultaneous channels, 16-bit nominal resolution, and per-channel sampling up to 200 kS/s; inputs support single-ended and differential topologies with integrated anti-alias filtering and input clamp protection in many modes. Explanation: simultaneous sampling simplifies multi-phase or multi-sensor capture (three-phase power, vibration arrays, motor currents) because channels share a synchronous conversion instant; integrated filters/protection reduce BOM and improve robustness in industrial DAQ and power-monitoring systems.

Key datasheet numbers to watch

Point: A focused checklist of canonical specs guides measurement plans. Evidence: primary numbers to track include SNR, ENOB, SINAD, THD+N, input range, input impedance, front-end filter characteristics, conversion timing and power consumption (typical vs min/max conditions). Explanation: these figures are typically reported under specific conditions (full-scale input, specified input frequency, nominal supply and temp). Always note whether a datasheet value is “typical” (measured on sample units under ideal lab conditions) or a guaranteed min/max (validated across process/temperature).

Common misconceptions and quick clarifications

Point: Several terms cause confusion when moving from spec sheets to bench results. Evidence: simultaneous sampling means simultaneous sampling by the ADC core — not necessarily identical front-end arrival times if your PCB traces differ. Nominal 16-bit resolution is not the same as 16-bit effective resolution. Explanation: ENOB (effective number of bits) quantifies usable resolution after noise and distortion; a device can be 16-bit nominal but deliver ~15.x ENOB under typical conditions. Similarly, input conditioning, buffer impedance and clock jitter often limit system-level SNR more than the ADC core itself.

2 — Core performance metrics explained (data analysis)

SNR, SINAD and ENOB: what they mean and how to interpret results

Point: SNR, SINAD and ENOB form the core trio for interpreting fidelity. Evidence: SNR measures signal power vs total noise (excluding harmonics), SINAD includes noise+distortion, and ENOB converts SINAD to equivalent bits via ENOB = (SINAD - 1.76) / 6.02. Explanation: use SNR to judge noise-limited performance and SINAD when harmonic distortion matters. For example, a measured SINAD of 95.5 dB converts to ENOB ≈ (95.5 − 1.76) / 6.02 ≈ 15.6 bits, indicating very high effective resolution for most industrial sensing tasks. When reporting results, always state test frequency, input amplitude (fraction of full-scale), windowing method and clock source.

THD+N and harmonic behavior for periodic inputs

Point: THD+N quantifies harmonic distortion relative to the fundamental and is crucial for periodic-signal fidelity. Evidence: THD measures harmonics (typically up to Nth order) while THD+N includes broadband noise; test tones at multiple amplitudes reveal linearity limits and intermodulation tendencies. Explanation: to assess THD+N for the device, use a low-jitter tone generator at several amplitudes (0 dBFS, −1 dBFS, −6 dBFS). Expect harmonic content to increase with amplitude and input front-end nonlinearity; small harmonic levels (−80 dB or better) are typical for high-quality 16-bit SAR ADCs under proper drive conditions. Note that THD+N requirements vary: power-harmonic detection tolerates higher THD than precision instrumentation.

Noise floor, dynamic range and spurious components

Point: The wideband noise floor and spurious tones set the lower limit for detectable signals. Evidence: quantization noise floor is theoretical based on bit depth, but real systems see added thermal and jitter-induced noise plus spurs from clock/feedthrough and channel crosstalk. Explanation: separate quantization-limited regions from real-noise-limited ones by sweeping input amplitude and observing noise spectral density. Spurs often align with clock harmonics or digital switching patterns on the PCB; crosstalk in simultaneous-sampling parts appears as correlated spurious content on neighboring channels when large signals are present. Mitigation begins with layout and clock discipline.

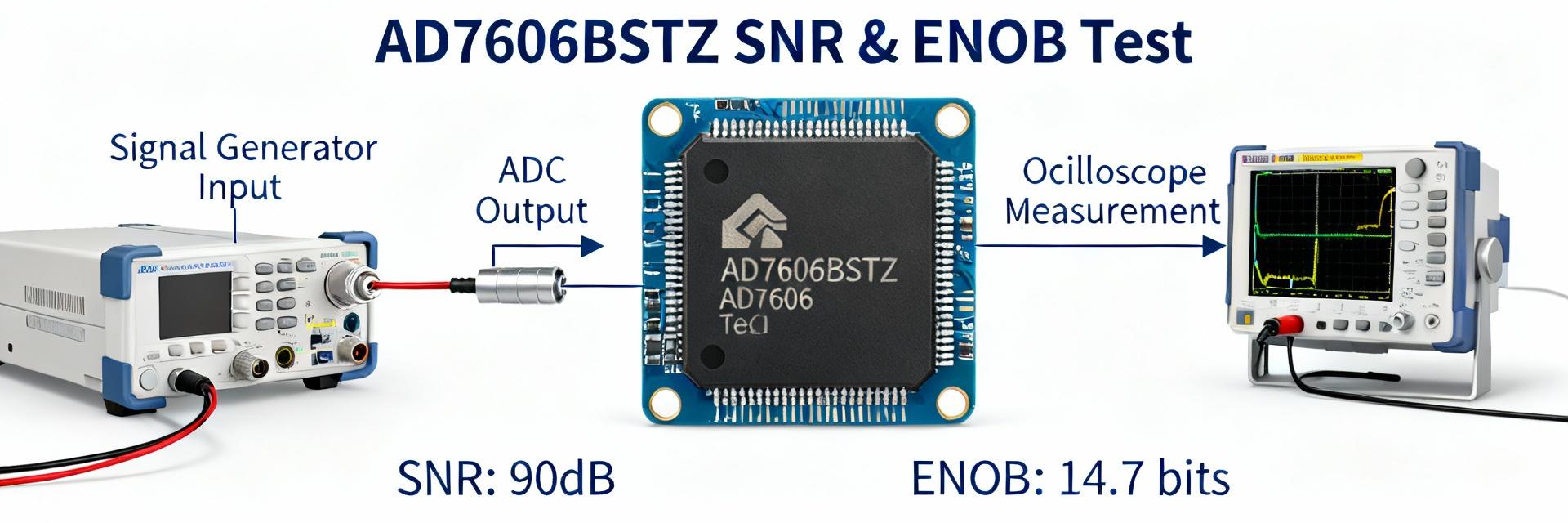

3 — Measurement & benchmarking methodology (method guide)

Recommended test setup and instruments

Point: A controlled, low-noise testbench is essential for meaningful ADC metrics. Evidence: recommended equipment includes a low-jitter signal generator, precision buffer or instrumentation amplifier, low-noise power supplies and references, an FFT-capable digitizer or the ADC-under-test with known capture and host; calibrated attenuators and well-shielded fixtures are mandatory. Explanation: the signal source jitter and front-end resistor noise often dominate SNR if not chosen carefully. Use a buffer with low input-referred noise and low distortion to drive the ADC full-scale; isolate digital and analog supplies, and route the clock with controlled impedance to minimize reflections and jitter pickup.

Measurement procedures and best practices

Point: Standardize steps to ensure reproducibility. Evidence: key steps include selecting DC/AC coupling, choosing amplitude (full-scale and reduced levels), enabling/disabling internal filters, choosing window type (e.g., Hann) and number of samples, capturing enough frames for averaging, and stabilizing temperature. Explanation: for SINAD/ENOB tests use single-tone inputs at several frequencies up to Nyquist/2 and at full-scale and −6 dBFS. For crosstalk measure inject a large tone into one channel while grounding or applying a small tone to an adjacent channel, observe spur amplitude referred to victim channel full-scale. Document clocking (internal/external), supply voltages and ambient temperature in all reports.

Data analysis & reporting templates

Point: Consistent plots and tables make comparisons valid. Evidence: include FFT magnitude (dB) with harmonic markers, noise spectral density (dBFS/Hz), ENOB vs frequency, THD+N vs amplitude, and time-domain alignment snapshots for channel sync. Explanation: always annotate plots with test conditions (input amplitude, frequency, window, sample count, clock jitter spec). Suggested table columns: input freq, amplitude (dBFS), SNR (dB), SINAD (dB), ENOB (bits), THD (dB), notes. Provide raw CSV or a reproducible script so peers can verify analyses.

4 — Comparative benchmarks and real-world use cases (case study)

Benchmarks: AD7606BSTZ vs. peer ADCs

Point: Comparative axes clarify trade-offs when selecting parts. Evidence: compare on SNR/ENOB, per-channel sampling rate, channel count, on-chip filtering/protection, power per channel and interface complexity. Explanation: in a normalized comparison, the AD7606BSTZ’s simultaneous sampling and integrated features favor multi-channel DAQ and power-analysis tasks, while some competitors trade channel count for slightly higher per-channel sample rates or different filter characteristics. Present normalized scores or radar charts to weigh the metrics that matter for your product decisions.

| Metric | AD7606BSTZ (typical) | Comparator A (example) | Comparator B (example) |

|---|---|---|---|

| Resolution | 16-bit | 16-bit | 16-bit |

| SNR / ENOB | ~95.5 dB / ~15.6 bits | ~92–94 dB / ~15.0 bits | ~96 dB / ~15.7 bits |

| Channels / Simultaneous | 8 simultaneous | 4–8 (multiplexed) | 8 simultaneous |

| Max sample / ch | 200 kS/s | 250 kS/s | 200 kS/s |

| On-chip filters/protection | Integrated anti-alias & protection | External filters often required | Some integrated options |

Use-case performance: industrial monitoring, power and vibration analysis

Point: Match metrics to application needs. Evidence: harmonic detection (power quality) requires low THD+N and high dynamic range; transient capture (inrush, switching events) needs sample rate and channel sync; vibration analysis favors low noise floor and consistent phase across channels. Explanation: for three-phase power analysis, simultaneous sampling ensures phase relationships are preserved and SNR ~95 dB yields accurate harmonic content to relatively high orders. For vibration arrays, consistent ENOB across channels and low crosstalk preserve modal analysis fidelity; confirm expected detection thresholds by injecting known small-amplitude tones and verifying SNR/noise floor in your final PCB assembly.

Trade-offs and selection guidance

Point: No single ADC is best for all designs — trade-offs drive choices. Evidence: factors include oversampling for improved SNR vs latency, aggressive filtering vs bandwidth, and power consumption vs sampling throughput. Explanation: prioritize low-latency simultaneous sampling for synchronized multi-phase capture; choose parts with integrated filtering if BOM reduction and robustness matter; select ADCs with scalable power modes if battery-powered or thermally constrained. Use a decision checklist weighing channel count, required ENOB at target frequency, allowed latency and system power budget.

5 — Design & optimization checklist for best ADC performance (actionable recommendations)

PCB layout, grounding and power integrity

Point: Layout often determines whether datasheet SNR is achievable. Evidence: star grounds, clear analog/digital split, local decoupling and ground pours reduce common-mode currents and high-frequency injection into analog nodes. Explanation: place decouplers within millimeters of supply pins, route analog returns to a single point near the ADC’s ground reference, and avoid routing noisy digital clocks over or under sensitive analog traces. Thermal vias under the package and proper ground stitching reduce thermal gradients and improve stability for long acquisitions.

Front-end conditioning: front-end amplifier, anti-aliasing and protection

Point: Properly sized anti-alias filters and input buffers preserve ADC linearity. Evidence: choose cutoff near 0.45–0.6 of Nyquist for minimal aliasing while retaining required bandwidth; use low-noise op amps with sufficient slew-rate and input range to drive the ADC over the full common-mode and differential input range. Explanation: use series source resistances and small RC or multi-pole filters as needed, balancing filter order with phase linearity. Input clamp protection should be placed to protect against faults but sized to avoid loading the signal at normal amplitudes.

Clocking, jitter management and oversampling strategies

Point: Clock jitter and reference noise directly reduce SNR at higher input frequencies. Evidence: low-jitter external clock sources and high-quality references maximize achievable SNR; oversampling and digital averaging can improve effective SNR at the expense of throughput. Explanation: prefer a low-phase-noise external clock when measuring high-frequency inputs; when using internal clocking, verify jitter specs and test at the same clock source intended for production. Oversampling followed by digital decimation reduces noise floor by √N for coherent averaging—useful when ultimate SNR matters more than real-time latency.

Summary

Point: Interpreting SNR, ENOB, THD+N and noise-floor figures in context yields realistic expectations for system performance. Evidence: datasheet typical numbers provide a baseline but bench measurements under your front-end, clock and layout conditions determine final results. Explanation: focus on reproducible measurement setups, control test conditions, and optimize layout/clocking to approach datasheet performance. The AD7606BSTZ performs strongly in multi-channel industrial DAQ roles when designed and tested with attention to input drive and clock discipline; use the measurement and optimization checklist above to validate system-level performance.

Key Summary

- The AD7606BSTZ delivers high SNR and near-16-bit effective resolution when tested under datasheet conditions; verify with controlled bench tests to confirm ENOB and SINAD.

- Measure SNR, SINAD, THD+N and noise spectral density with low-jitter sources and proper windowing; document input amplitude, frequency, clock and temperature for reproducibility.

- Layout, grounding and front-end buffering are the most common causes of degraded ADC performance—follow star-grounding, short analog traces and local decoupling.

- For multi-channel tasks (power, vibration), simultaneous sampling preserves phase relationships; weigh filter cutoff, oversampling and latency trade-offs per application needs.

- Report ENOB using ENOB = (SINAD − 1.76) / 6.02 and include test notes so peers can replicate and validate your results.

Common Questions

How do I verify ENOB for the AD7606BSTZ in my system?

Measure SINAD with a low-jitter single-tone source at several frequencies and amplitudes; compute ENOB = (SINAD − 1.76) / 6.02. Ensure input drive is low-noise and matched to the ADC’s input range, document clock source/jitter and use windowing with sufficient samples. Repeat tests at full-scale and reduced amplitudes to see linearity and noise-limited regions.

What input filtering is recommended to meet ADC performance metrics?

Place anti-alias filters with cutoff around 0.45–0.6 × Nyquist to balance alias suppression and bandwidth. Use low-noise buffers ahead of the ADC if source impedance is high, and prefer multi-pole filters only when phase shift is acceptable for your application. Protect inputs with clamps rated to avoid loading under normal conditions while guarding against fault events.

How do I isolate crosstalk in simultaneous multi-channel captures?

To measure channel-to-channel crosstalk, inject a large amplitude tone on one channel and measure spurious energy on neighboring channels; reduce crosstalk via shorter analog traces, careful routing of return paths, analog ground pours and decoupling. Avoid routing digital lines near sensitive analog inputs and ensure synchronous capture timing to attribute correlated spurs correctly.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- MAX3232CPWR Performance Report: Real RS-232 Specs & Insights

- 74HC123PW Complete Specs & Datasheet Quick-Reference

- SN74HC126PW Availability: Technical & Stock Snapshot

- SN74HC126PW Datasheet Deep Dive: Key Specs & Tests

- MAX96712GTB/V+T Availability and Pricing: Market Report

- ADS1015 ADC Deep Specs Report: Pinout & Performance

- Marvell 88SE9235A1 Deep Specs & Real-World Benchmarks

- STM32F103C8T6 Blue Pill: Benchmarks & Field Results

-

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP

HCPL2601onsemiOPTOISO 2.5KV OPN COLL 8-DIP -

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP

MCT6onsemiOPTOISOLATOR 5KV 2CH TRANS 8-DIP -

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T

C3PPT-2618MCW IndustriesIDC CABLE - CPC26T/AE26M/CPC26T -

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T

C3PPT-2606GCW IndustriesIDC CABLE - CPC26T/AE26G/CPC26T -

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2636GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2618GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T

C3EET-5036GCW IndustriesIDC CABLE - CCE50T/AE50G/CCE50T -

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G

C3AAG-2606GCW IndustriesIDC CABLE - CSC26G/AE26G/CSC26G -

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X

C1EXG-2636GCW IndustriesIDC CABLE - CCE26G/AE26G/X -

S6008LLittelfuse Inc.SCR 600V 8A TO220

S6008LLittelfuse Inc.SCR 600V 8A TO220