STM8S003F3U6TR Datasheet: Key Specs, Pinout & Quick PDF

2026-04-11 12:57:06

0

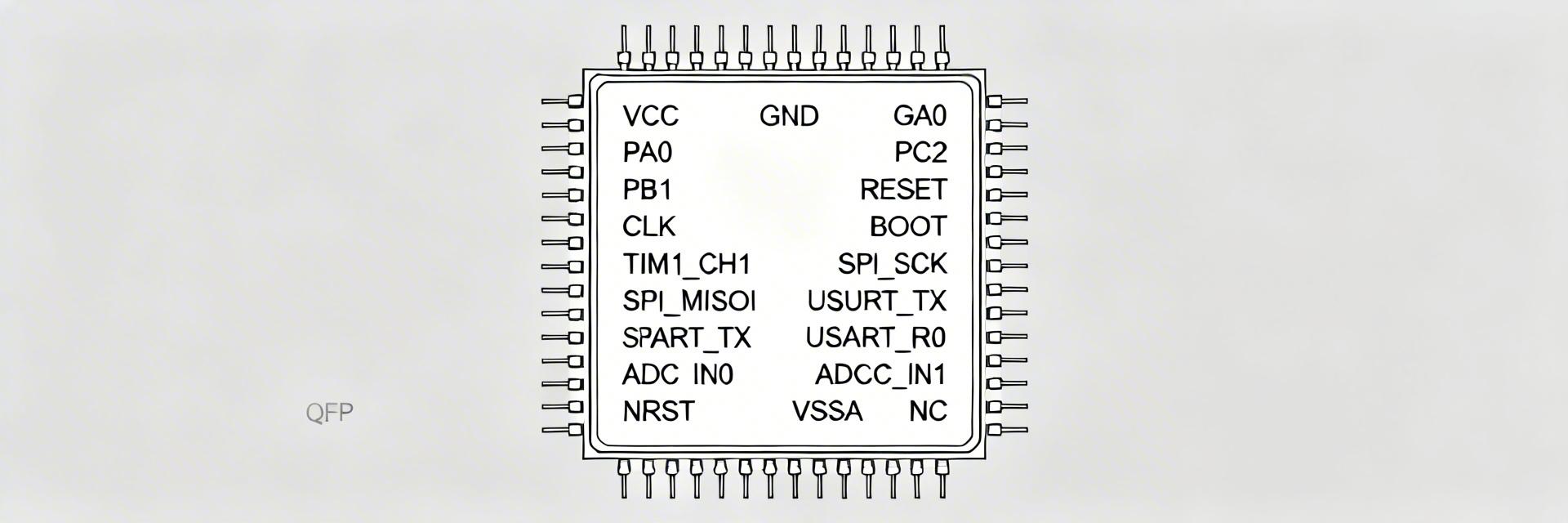

Key Takeaways Cost-Efficiency: Industry-leading 8-bit price-to-performance ratio for mass production. Flexible Power: Supports 2.95V to 5.5V, simplifying BOM by removing regulators. Compact Design: TSSOP20 package reduces PCB footprint by 30% vs. DIP alternatives. Reliable Lifecycle: STM8S core ensures long-term availability and predictable performance. The low-cost 8-bit MCU segment remains dominant in simple embedded controls, driven by predictable performance, tiny footprints, and minimal BOM impact. For engineers choosing parts, the datasheet is still the fastest way to validate constraints and avoid rework. This compact guide focuses on the STM8S003F3U6TR datasheet and delivers a short, actionable route to the official PDF, the most relevant key specs, and a clear pinout reference to get a board from schematic to layout quickly. 1 — Overview & Typical Applications (Background) — What this MCU is (core identity & role) Point: The part is a budget 8‑bit microcontroller intended for simple control and measurement roles. Evidence: It belongs to a family optimized for low cost and small footprints. Explanation: Designers pick this class for basic serial control, simple ADC sampling, timed outputs, and low-pin-count consumer functions because the MCU balances flash/SRAM and peripheral set against price and power. — Typical use cases and target designs Point: Typical applications leverage cost and footprint advantages. Evidence: Common real-world fits include sensor nodes with infrequent sampling, simple motor or LED drivers, consumer appliance controllers, and hobby/dev boards. Explanation: Selection drivers are usually cost, required GPIO count, package size, and whether a small ADC or timer set is sufficient for the control loop. Competitive Differentiation Feature STM8S003F3U6TR Generic 8-bit (Competitor) User Benefit EEPROM 128 Bytes True Data Emulated (Flash) Higher endurance for settings storage Operating Voltage 2.95V to 5.5V 1.8V to 3.6V only Works directly with 5V industrial rails Clock System Internal 16MHz (1% drift) Internal 8MHz (3% drift) More stable UART/Serial timing 2 — Key Specs at a Glance (Data analysis) Point: Rapidly validate feasibility by scanning core, clock, memory and voltage ranges. Evidence: The table below lists the fields you should confirm in the official PDF; values shown are representative—always cross-check the datasheet for exact numbers. Explanation: These fields answer the basic integration questions: can the MCU hold firmware, run at required speed, and tolerate your power rails? Field User Benefit / Value Core type / bitsSTM8 family, 8‑bit efficiency Max clockUp to 16 MHz (Handles complex math faster) Flash8 KB (Large enough for RTOS-lite) SRAM1 KB Data EEPROM128 B (Saves user settings permanently) Operating voltage2.95–5.5 V (Flexible power supply) Temperature range−40°C to +85°C (Industrial Grade) Typical currentsActive: low mA; Standby: µA range (Battery friendly) PRO INSIGHT Engineer's Design Checklist by David Zhang, Senior Hardware Architect 1. The "VCAP" Gotcha Unlike many 8-bit MCUs, the STM8S requires a 1µF low-ESR ceramic capacitor on the VCAP pin for internal regulator stability. Missing this is the #1 reason for "dead" boards. 2. SWIM Routing Keep the SWIM (Single Wire Interface Module) trace short. If routing through a connector, ensure a 10k pull-up is present to prevent noise-triggering resets during production. STM8S MCU 1uF VCAP Hand-drawn sketch, not an exact schematic / 手绘示意,非精确原理图 3 — Pinout & Package Details (Method guide) — Pin mapping: how to read the pinout diagram Point: Understanding multifunction pins prevents early routing mistakes. Evidence: A labeled pinout diagram makes VCC/GND, RESET, oscillator, VREF, debug and high‑priority GPIOs obvious. Explanation: When reading the pinout, mark power pins, dedicated reset/boot pins, and pins with alternate ADC/UART/SPI functions; note which pins are shared with debug so they aren’t permanently assigned if you need in-circuit programming. — Package mechanicals & footprint guidance Point: Mechanical drawing dimensions dictate PCB land pattern and clearances. Evidence: Pull the mechanical table from the datasheet for exact footprint numbers and tolerances. Explanation: Follow recommended land pattern, place decoupling capacitors close to VCC pins, reserve clearance for oscillator components, and add small test pads for critical signals to ease manufacturing debug. 4 — Electrical Characteristics & Performance (Data analysis) — Operating conditions & limits (how to read the tables) Point: Distinguish recommended conditions from absolute maxima to avoid damage. Evidence: Datasheets separate recommended operating conditions (where guaranteed behavior applies) and absolute maximum ratings (limits that cause irreversible damage). Explanation: Note IO pin clamp voltages, absolute VCC limits, and per-pin current. A common omission is neglecting combined current into VCC when many outputs source at once—add a safety margin to thermal and current budgets. Rating type Design action Absolute maximum voltagesDo not design to these; they are destructive limits Recommended operatingDesign and validate here for reliable operation — Timing, clocks & common performance trade-offs Point: Clock choice affects power and timing. Evidence: Datasheets list internal RC and external crystal options, boot/reset timing and ADC sample times. Explanation: Internal oscillators save cost but vary with temperature; crystals improve timing at cost of parts and board area. For low-power designs, choose lower clock or sleep modes and verify wake-up timing vs your application latency needs. Note the section titled electrical characteristics for specific timing numbers. 5 — Quick PDF download, a short example & design checklist (Case + Action) — Quick PDF download checklist & filenames Point: Find the official PDF on the manufacturer's product documentation page. Evidence: Use the product page or documentation center to download the official datasheet PDF. Explanation: Quick-scan checklist: search within the PDF for "electrical characteristics", "pin description", "package drawing", "memory map", and "application notes". Download the STM8S003F3U6TR datasheet PDF to jump straight to these sections. — Quick start example & practical PCB/firmware tips Point: A minimal bring-up checklist gets you to a blinking LED quickly. Evidence: Common steps used by engineers at first power-up are power decoupling, reset pull, oscillator selection, and mapping a single GPIO to an LED. Explanation: Example pseudocode: configure GPIO as push-pull output, toggle with 500 ms delay. Key design tips follow below and a small power+reset schematic is included for reference. Place 0.1 µF decoupling capacitor within 1–2 mm of VCC pins; add 10 µF bulk near regulator. Use a clean reset pull-up and a 10 kΩ resistor; add a capacitor only if specified in datasheet. Avoid assigning debug/program pins to permanent functions if in-circuit programming is needed. Keep ADC input traces short, shielded from noisy digital lines, and use single‑point ground near VREF. Check thermal derating if many outputs source/sink current simultaneously. Before routing, verify alternate functions for multifunction pins to prevent conflicts. Summary ✓ Where to download: Use the manufacturer's product documentation page and the PDF anchor above to access the STM8S003F3U6TR datasheet quickly. ✓ Top 3 specs: Flash/SRAM capacity, operating voltage/current, and peripheral count define your design feasibility. ✓ Single most important PCB tip: Place decoupling caps and the VCAP capacitor as close to the MCU as physically possible. FAQ How do I get the STM8S003F3U6TR datasheet? Download it from the manufacturer's product documentation page or your internal documentation server. Look for the PDF named for the part family and use the quick-scan checklist above for fast validation. What are the critical STM8S003F3U6TR key specs to verify before design? Confirm flash and RAM size (8KB/1KB), the operating voltage range (up to 5.5V), and the peripheral set. Also, verify current consumption if your device is battery-powered. Where can I find the STM8S003F3U6TR pinout diagram and footprint details? The official datasheet PDF contains the pinout diagram and the mechanical drawing table with recommended TSSOP20 land pattern dimensions.

READ MORE